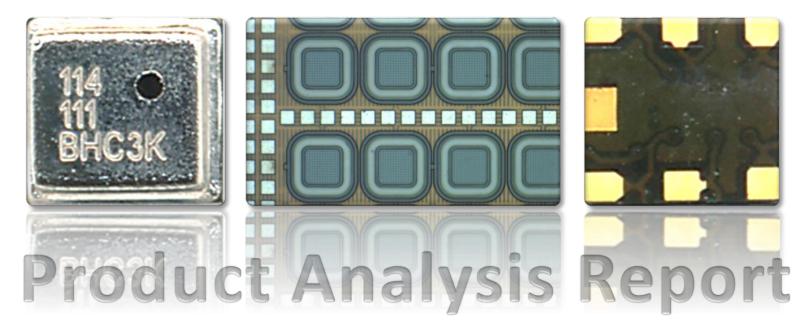

## **CMOS-MEMS** Pressure Sensor

This report is protected by copyright and may not be by way of trade or otherwise, be copied, reproduced, re-sold, lent, hired out in any form without express written permission from Shanghai Industrial µTechnology Research Institute(Hereinafter referred to as SITRI).SITRI always endeavors to provide accurate and reliable information to its customers. However, it is not possible to guarantee absolute accuracy of all information contained herein and SITRI can assume no liability for inadvertent errors in this report.

This report was prepared for our Clients' private study, analysis or research and for no other purpose. The information contained in this report may describe technical innovations, which are the subject of patents held by third parties. The disclosure by SITRI of any such information is in no form whatsoever an inducement to infringe any patent. SITRI assumes no liability for patent infringement arising from the use of the information contained in this report.

www.sitrigroup.com

## **Table of Contents**

| Device Summary3                                | Capacitor Cross Section |

|------------------------------------------------|-------------------------|

| Device Summary                                 | SEM Image and           |

| Package Overview4                              | Thickness of Cor        |

| Top Bottom Side View with Measurement          | Measurement o           |

| Die Information5                               | SEM Image and           |

| Die Photo with Measurement                     | Process Compar          |

| Die Corner Image                               |                         |

| Pad Size                                       | EDS Analysis            |

| General Structure8                             | EDS Analysis for        |

| Die Thickness                                  | EDS Analysis for        |

| Each Layer Structure and Thickness Measurement | EDS Analysis for        |

| Gate Length of Poly Gate                       | Major Findings          |

| Capacitor Plan View14                          | Summary of PS1          |

| Plan View of Capacitor and Dimension           |                         |

| SEM Image and Measurement of Capacitor         |                         |

|                                                |                         |

| Capacitor Cross Section23                                  |

|------------------------------------------------------------|

| SEM Image and Measurement of Cross Section of Capacitor    |

| Thickness of Conductive Plate                              |

| Measurement of Cavity between Conductive Plates            |

| SEM Image and Measurement of Cavity Release Hole           |

| Process Comparison between Different Capacitor-Y Direction |

| DS Analysis40                                              |

| EDS Analysis for Capacitor Upper Conductive Plate          |

| EDS Analysis for Capacitor Lower Conductive Plate          |

| EDS Analysis for Cavity Release Hole                       |

| Лаjor Findings43                                           |

| Summary of PS1606?                                         |

|                                                            |

T