####

# Where is the Packaging Technology Drifting? : Speed/Flexibility

Choon Lee I COO and CTO

# Agenda

# Technology trend

# Amkor packaging solution

# New society proposal

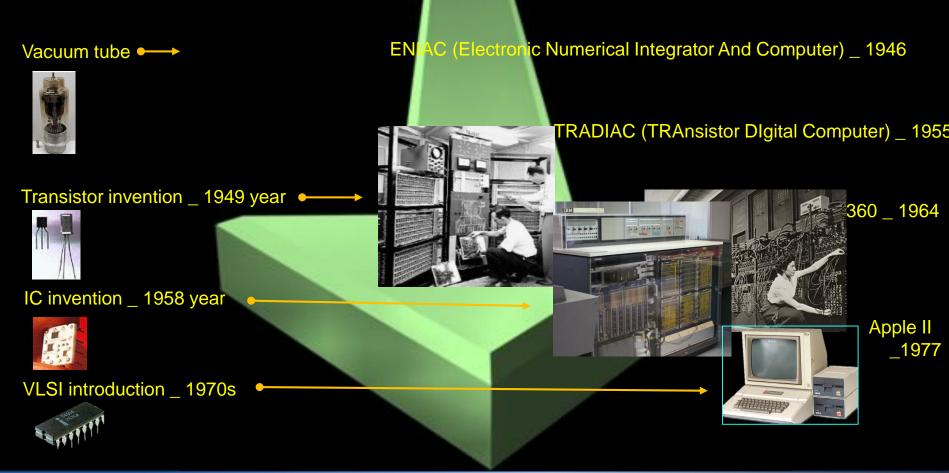

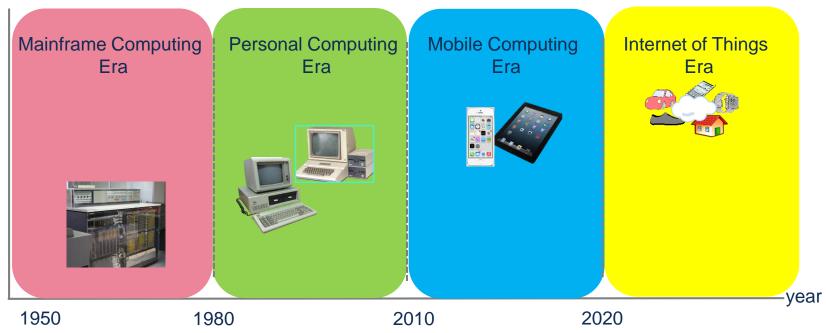

# **Computing trend**

#### market

# New growth driver

자료: HMC투자중권.

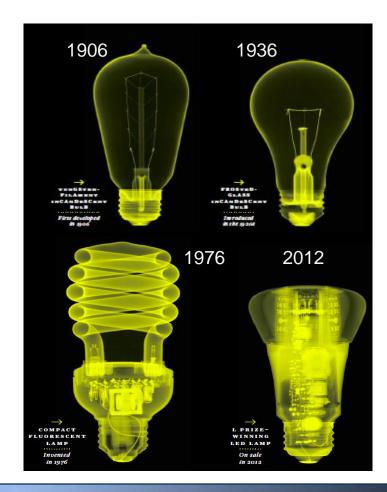

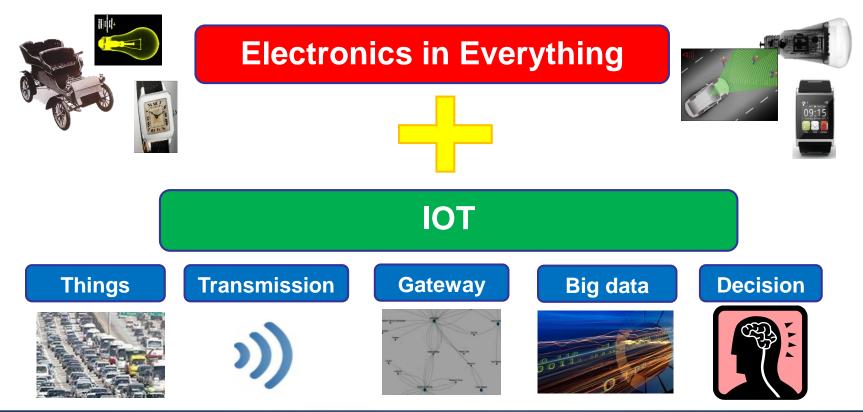

# Electronics in Everything – The Light Bulb

- For 70+ years the common light bulb contained no electronics

- Then in the 1970's, CFL bulbs included a small power converter.

- Today the LED bulb contains a power supply, driver circuits, dimmers, etc.

- Soon bulbs will contain WiFi or Bluetooth radios and microcontrollers for remote operation.

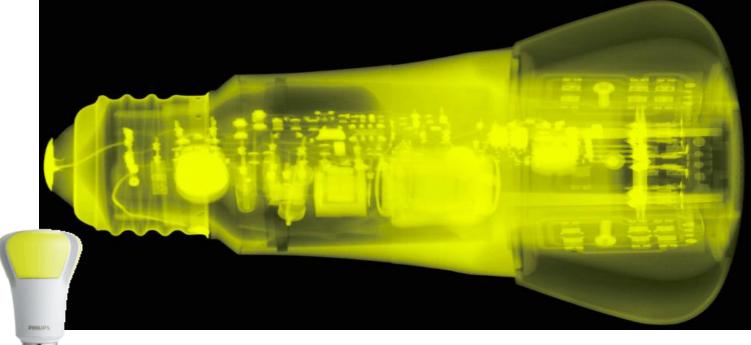

# X-ray Image of the L-Prize Winning LED Lamp

**Philips Lighting**

Glows white when illuminated

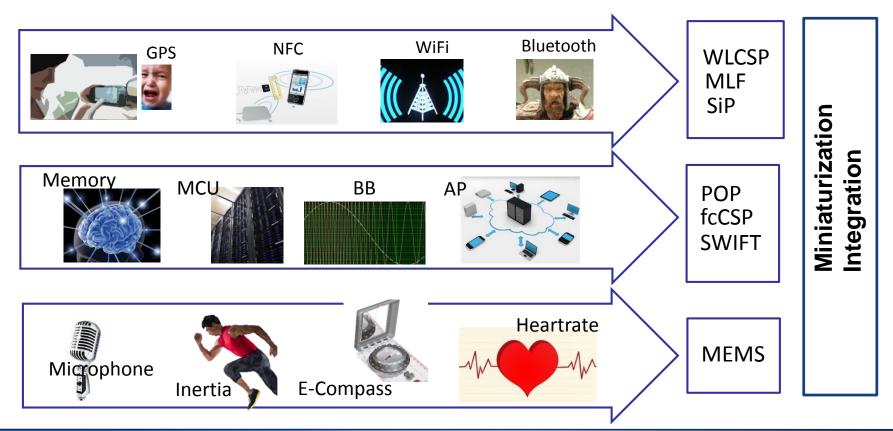

# **Q)** What's the packaging solution for IoT era?

# A) The answer is Miniaturization and Integration !

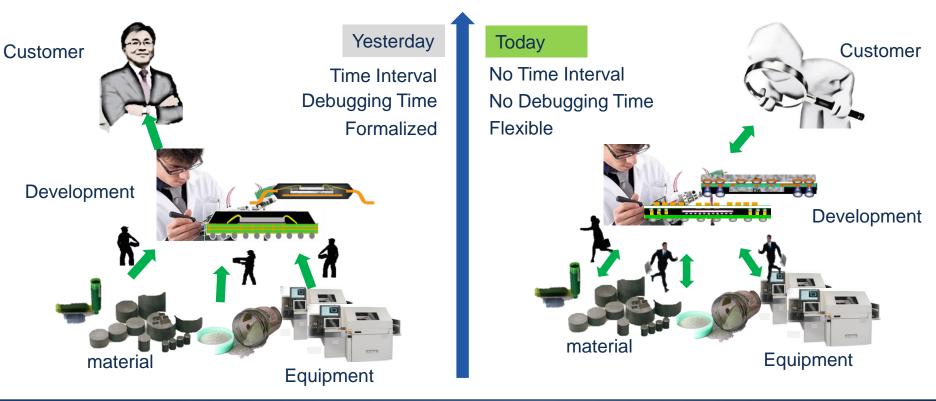

# **Q)** What's the technology solution for new development paradigm?

# A) The answer is wide packaging experience and process readiness !

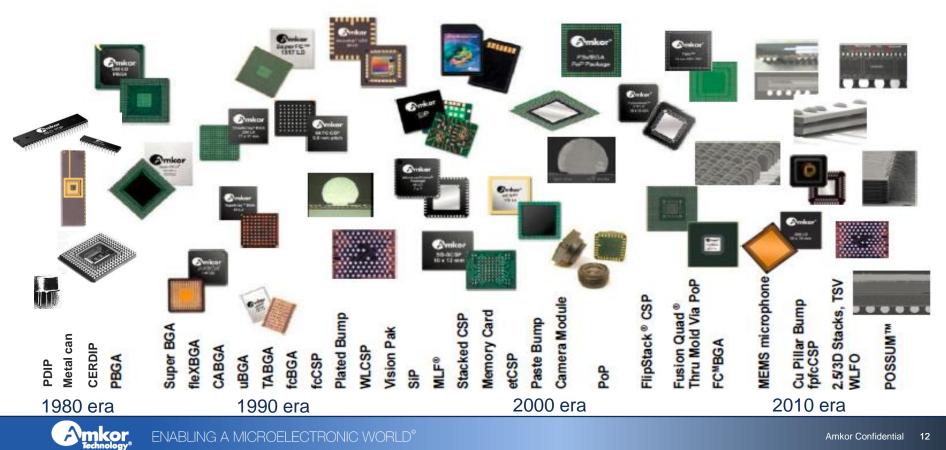

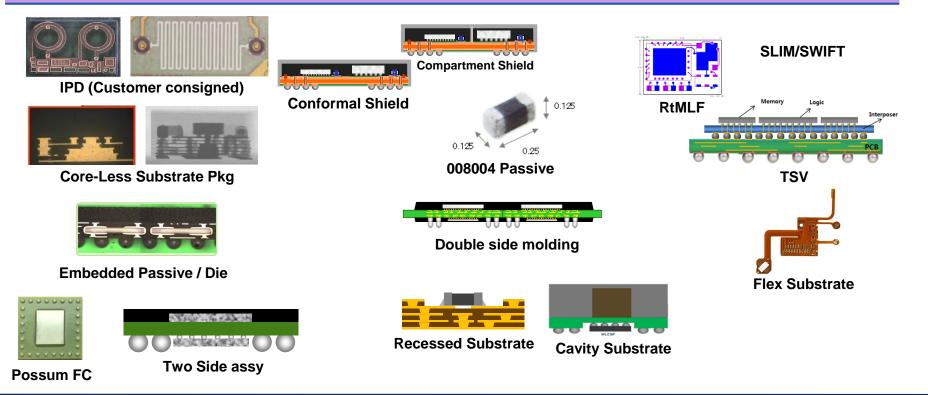

## **Amkor Packaging Experience**

## **Amkor One-stop and Total Solution**

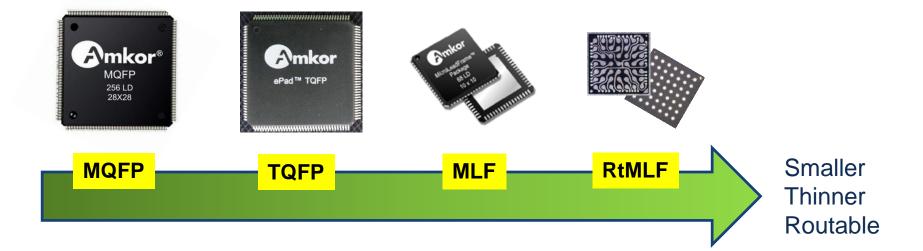

#### Leadframe Package Innovation

• Even matured leadframe package, the innovation named routable is achieved

-

Routable

Out pad

## RtMLF (Routable MLF)

- What is RtMLF?

- Resin filled trace available 1L substrate(MLF)

- Low cost and small form factor driven structure

- For server, PC, game console as well as mobile peripheral

- Interconnection method

- Wire Bonding, Flip Chip

- Development status

- Body size : ~10x10mm

- I/O count : ~176

#### Wire Bonding

Flip Chip

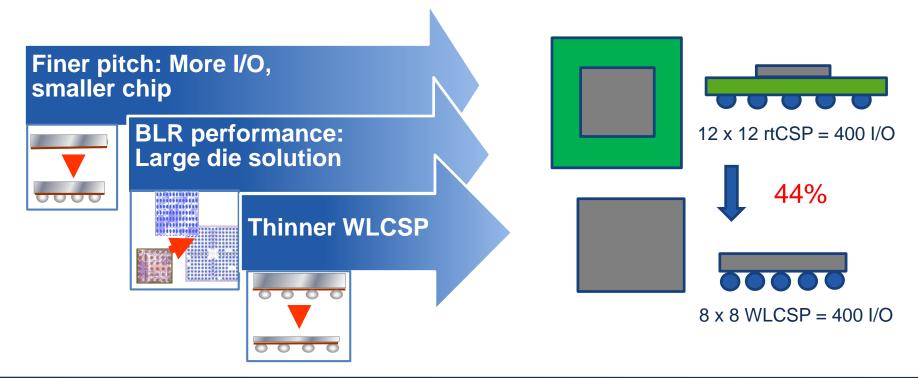

# **WLCSP** is moving

Mid I/O packages are converted to WLCSP due to form factor/cost

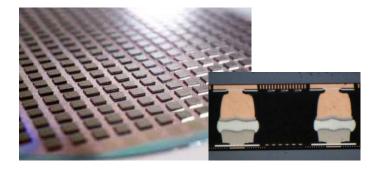

## **WLCSP Large Die Solution**

WLCSP with mold structure is to improve solder joint performance

| CSP <sup>nl</sup> + Mold                          |          |           |           |            |          |           |          |           |

|---------------------------------------------------|----------|-----------|-----------|------------|----------|-----------|----------|-----------|

|                                                   | BD size. | Die thick | Ball size |            | ТС       |           | Drop     |           |

| EMC                                               | (mm)     | (um)      | (um)      | Ball Alloy | 1st fail | Mean life | 1st fail | Mean life |

| Polyimide 2 Cu UBM                                | 10×10    | 250       | 250       | SACQ       | 1225     | 2849      | 179      | 1228*     |

| Plated Cu RDL Polyimide 1<br>Customer Passivation | 10x10    | 350       | 250       | SB05       | 836      | 1944      | 251      | 1442*     |

| Silicon                                           |          |           |           |            |          |           |          |           |

BLR performance Driven

\* Mean life is extrapolated because failure ratio is less than 50%

# New Concept Technology without TSV

- Higher Performance

- Integration

- Cost benefit

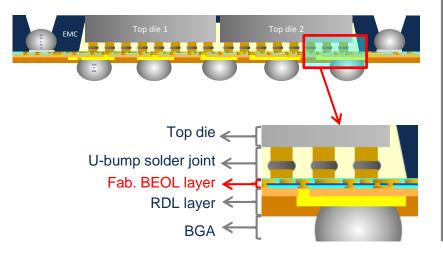

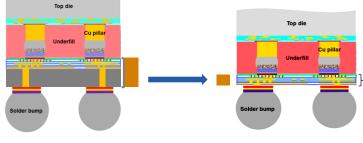

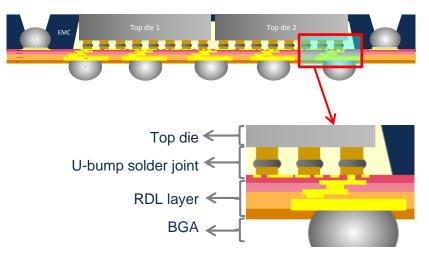

# SLIM™

Silicon-Less Integrated Module

# SWIFT<sup>™</sup>

#### Silicon Wafer Integrated Fan-out Technology

# SWIFT covers Flip Chip CSP and SiP application

#### Tall Cu pillar for memory interface 180um tall Cu demonstrated -Molded 12inch CoW wafer processing - Available Fine pitch u-bump interconnection CoW chip attach with mass reflow -Fine L/S multi RDL 40/45um available Backside pattern reveal and carrier attach 5/5um available 30um demonstrated Available 3L RDL demonstrated

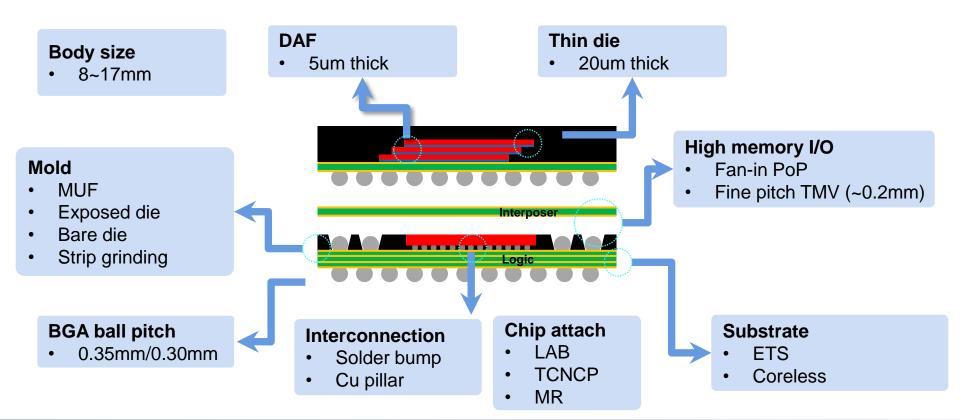

# Logic and Memory package stack

# **Thin PoP Roadmap**

(max thickness)

|                                                                                                     | Available | 2015 | 2016 | 2017 |

|-----------------------------------------------------------------------------------------------------|-----------|------|------|------|

| Memory thickness (assumption)                                                                       | 0.43      | 0.39 | 0.36 | 0.35 |

| <ul> <li>Exposed die TMV</li> <li>Bottom PKG thickness</li> <li>Total stack-up thickness</li> </ul> | 0.69      | 0.60 | 0.51 | 0.48 |

|                                                                                                     | 1.12      | 0.99 | 0.87 | 0.83 |

| <ul> <li>Bare die TMV</li> <li>Bottom PKG thickness</li> <li>Total stack-up thickness</li> </ul>    | 0.69      | 0.65 | 0.63 | 0.62 |

|                                                                                                     | 1.12      | 1.04 | 0.99 | 0.97 |

| <ul> <li>Interposer TMV</li> <li>Bottom PKG thickness</li> <li>Total stack-up thickness</li> </ul>  | 0.71      | 0.65 | 0.61 | 0.59 |

|                                                                                                     | 1.20      | 1.10 | 1.04 | 1.00 |

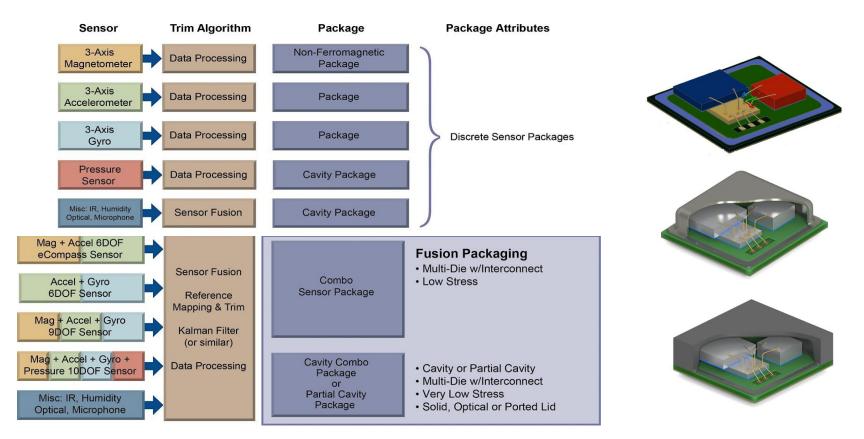

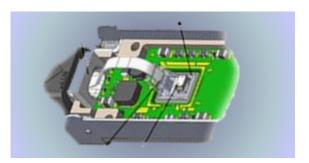

# Packaging Trend in Sensors is Going to Fusion!

# **MEMS / Sensor Products**

## **SiP Requirement**

# **Advanced SiP Design Guideline**

| Item                     | Production | Development                                 |                                   |

|--------------------------|------------|---------------------------------------------|-----------------------------------|

| Die to PKG Edge          | 85         | 75                                          | 01005                             |

| Comp. pad to PKG edge    | 85         | 75 01005<br>Comp. to Comp.<br>distance 85um | Comp. to Comp.<br>distance 60um   |

| Die to Die               | 75         | 65 (Non-common net)                         | (Common net)                      |

| Non common net Comp. pad | 85         | 75 Die to die                               | 0201<br>Comp. to Comp.            |

| Common net Comp.         | 60         | 50 distance 75um                            | distance 85um<br>(Non-common net) |

| Metal trace to Comp.     | 80         | 70 0201 Comp. to                            |                                   |

|                          |            | Comp. distance<br>60um<br>(Common net)      | Die to Comp.<br>distance 75um     |

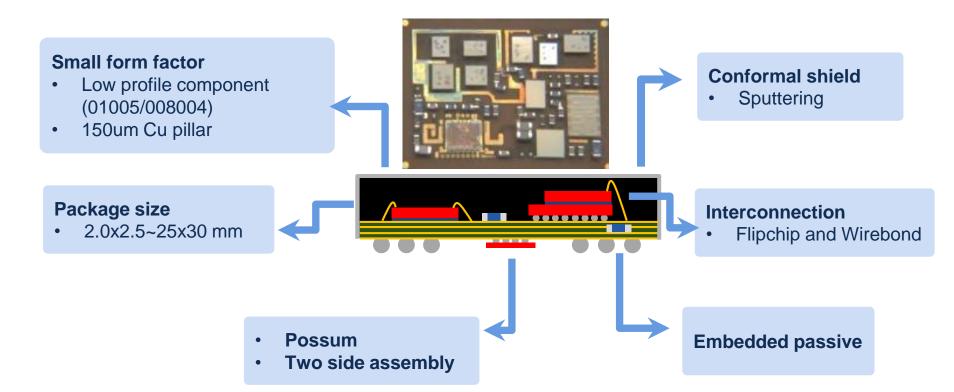

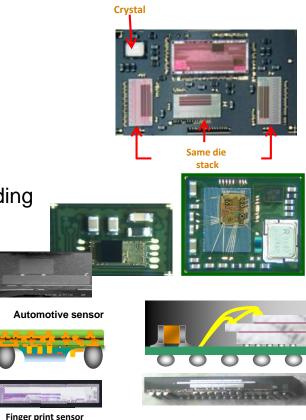

# **Amkor's Experience with Varying End Applications**

- Memory

- Same die stack, Pyramid stack, side by side MCM

- DAF, FOW, Wire Bonding Interconnection

- Connectivity, Digital, Consumer

- WLCSP (FC die) and Wire Bond Stack, Crystal

- FC+ 2 die stack, die to die bonding, die to PCB bonding

- MUF (Mold Under Filling)

- Automotive, Sensor

- Sensor Die expose Film assist molding

- Double side assembly, Possum FC die

- TSV, CoC stack

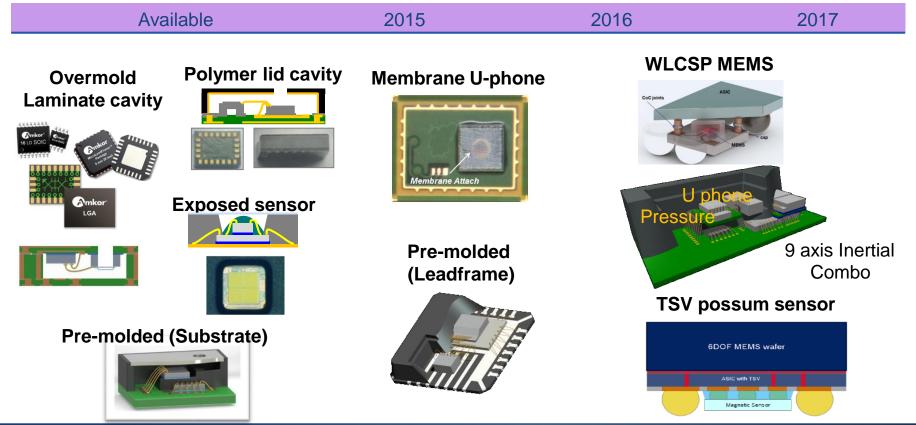

# **SiP Technology**

#### **Available**

#### 2015

2016

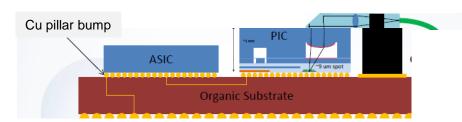

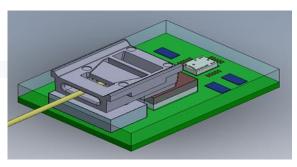

## **Si Photonics**

# **Technologies for Photonics**

#### Chip on wafer technology

#### System in Package technology

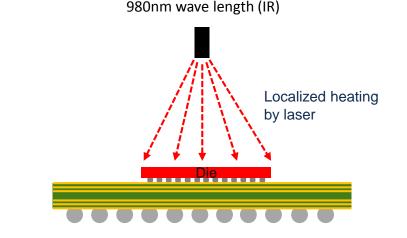

# LAB (Laser Assisted Bonding) Technology for lower stress attach

- New interconnection solution using laser beam after F/C bonding

- Only die heat up with area laser (Local reflow concept)

- Low thermal stress between PCB and die

- Fast solder melting : High UPH (Same as mass reflow)

#### Target markets

- Mobile, networking, consumer, CPU/GPU

- BB, AP, logic, ASIC

- Low K device (28nm, 20nm, 14/16nm)

#### Technology advantage

- Cost effective process

- Lower thermal stress than mass reflow

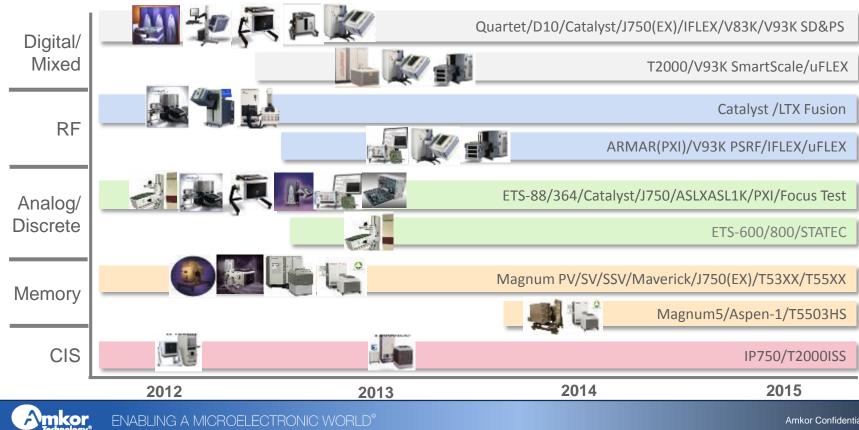

## **Amkor Tester Availability**

Amkor Confidential 31

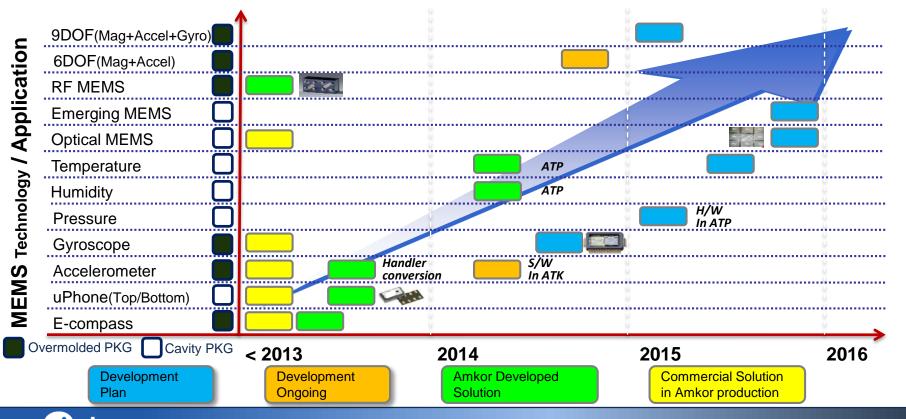

## **Amkor MEMS Tester Development**

ENABLING A MICROELECTRONIC WORLD®