# Mobile Phone RF Front End Integration Roadmap

March 17, 2015 James P Young

#### Agenda

- Market Dynamics

- Smartphone Front End Block Diagram

- Block By Block Performance Analysis (SOC vs. SIP)

- RF Switch

- PA

- Analog and Mixed Signal

- MIPI: Gate Level

- ESD

- Isolation Requirements

- Top Level Tools and Simulation Requirements

- Summary

Market Dynamics

#### **Connect Everything**

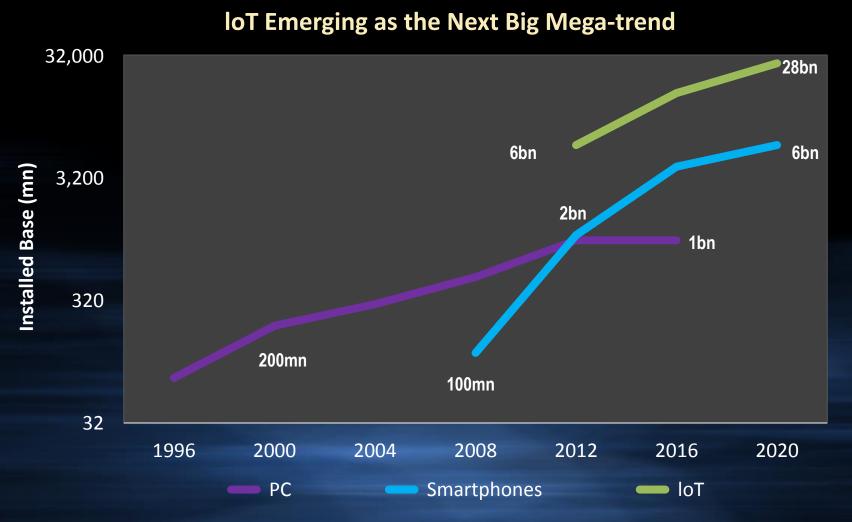

#### **Connected Devices Are Exploding** SKYWORKS

Y-axis is on a logarithmic scale

Source: IDC, Ericsson, Goldman Sachs Global Investment Research

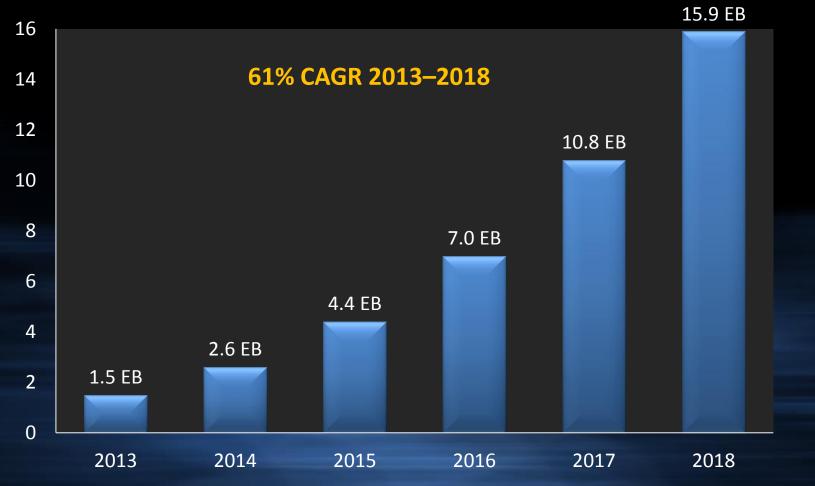

#### **Global Mobile Data is Exploding**

**Exabytes Per Month**

Source: Cisco VNI Mobile, 2014

|                       | 2012       | 2014       | 2016E     | 2020E  |

|-----------------------|------------|------------|-----------|--------|

| LTE Rel               | LTE Rel-11 | LTE Rel-12 | LTE Rel-X | 5G     |

| # CA Bands            | 2          | 3          | 3         | 5      |

| мімо                  | 8x8        | 8x8        | 8x8       | 64X8   |

| Proposed<br>New Bands |            | 5+         | 24        | 50     |

| CA Band<br>Combos     | 25         | 75+        | 172       | 300    |

| Peak/Max DL           | 1.2Gbps    | 3Gbps      | 6Gbps     | 18Gbps |

Increasing Front End Complexity

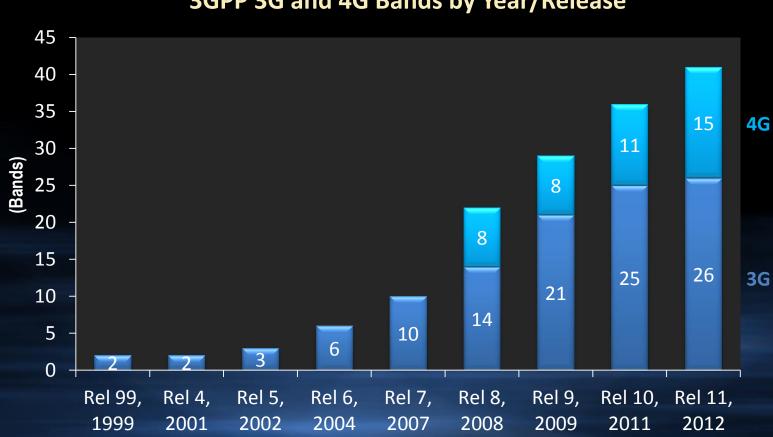

#### **Expanding Band Count**

**3GPP 3G and 4G Bands by Year/Release**

More Data = More Bands

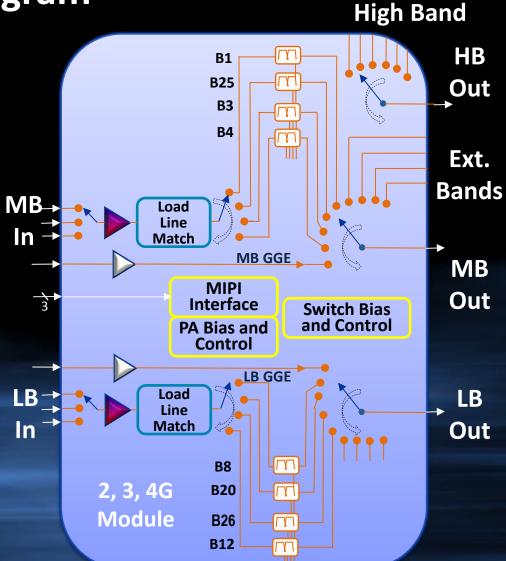

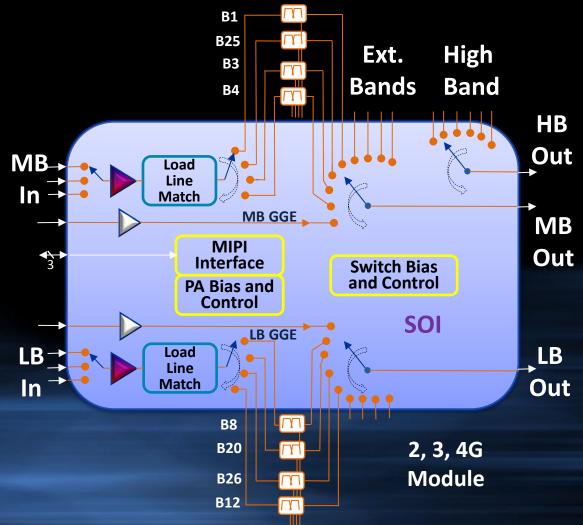

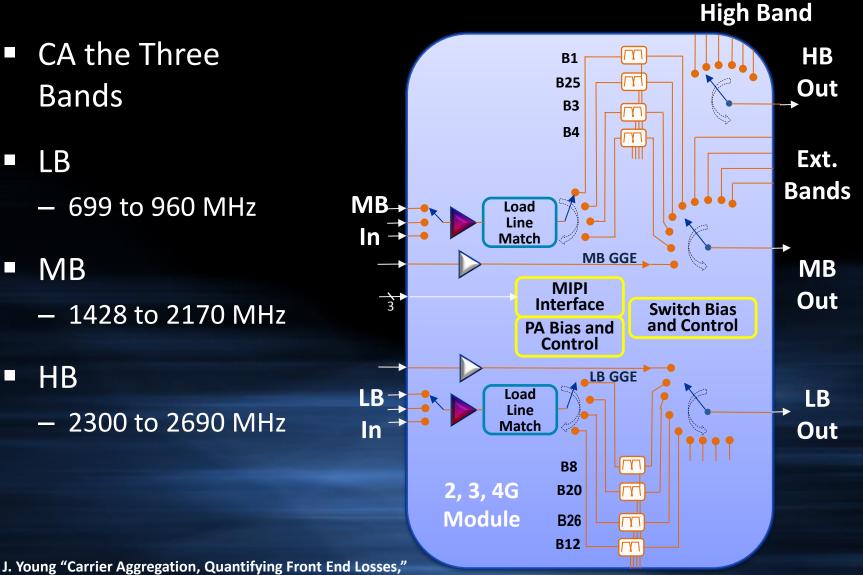

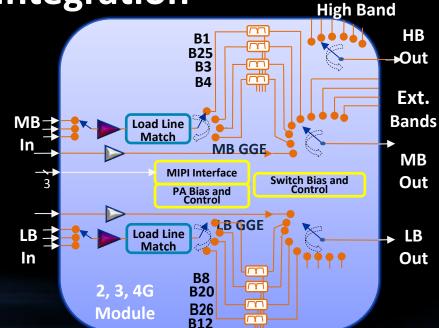

# Cellular Smartphone Front End Block Diagram

#### Mobile Handset Front End Block Diagram

- Smartphone

- 2, 3, and 4G

- 14 + Bands Typ.

- LB 699 to 960 MHz

- MB 1428 to

2170 MHz

- HB 2300 to

2690 MHz

- Assumes High Band Module is Separate, but Could be Integrated

**SKYWORKS**<sup>®</sup>

# Mobile Handset FE Circuit Blocks

- RF Switch

- Switch Control

- PA

- 4 to 6

- Harmonic terminations

- Load line match

- PA Control

- MIPI RFFE

26 to 52 MHz SPI

Everything in Blue Could Be in SOI, But Should It Be?

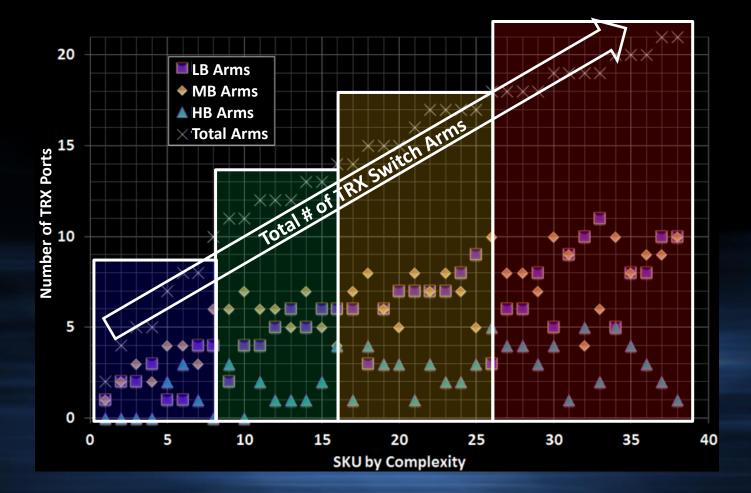

# **RF** Switch

#### RF Switch Complexity in LTE World: Increasing Number of Bands

**Total Switch Arms Required are Increasing**

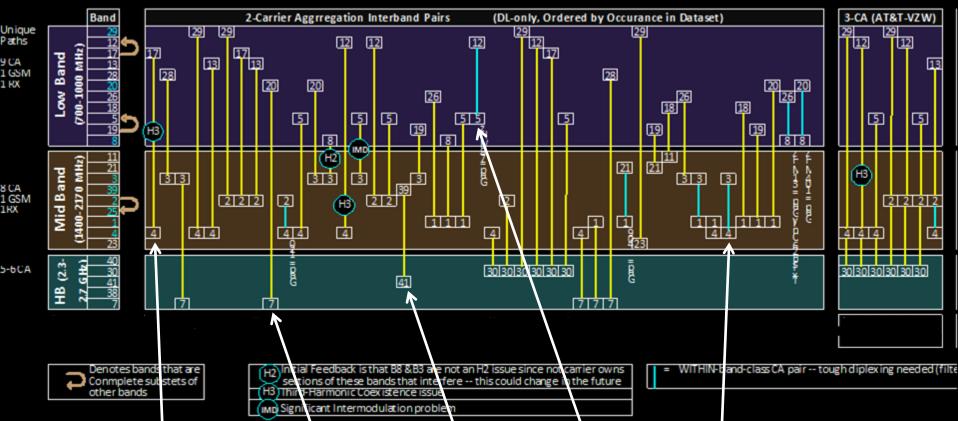

#### Inter-band Carrier Aggregation Simultaneous Transmission of Multiple Bands

**SKYWORKS**<sup>®</sup>

Low/Mid, Low/High, Mid/High, Low/Low, Mid/Mid

Low/Mid/High

**RF Switch is Partitioned by Band to Allow for Diplexing of Bands**

IWPC Chicago Meeting Sept. 16, 2014

LB

# **Front End Block Diagram**

**SKYWORKS**<sup>®</sup>

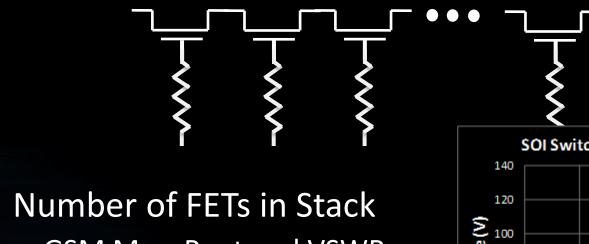

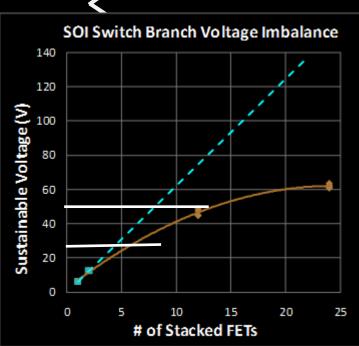

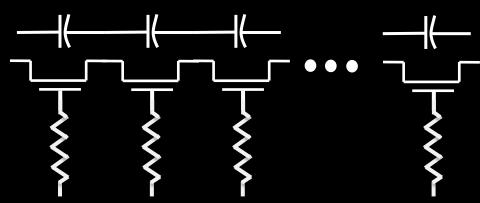

#### Antenna Switch/Tuner Design

- GSM Max. Pout and VSWR

- ≈53Vp

- 3/4G Max. Pout and VSWR

- ≈25Vp

- Each FET Can Sustain?

- Technology dependent

- Sub parasitics cause voltage imbalance

Peak RF Voltage Determines the FET Stack

#### Antenna Switch/Tuner Design

- Having established the number of FETS in the stack

- Minimize Coff to achieve specified off isolation

- Use minimum L and scale W to specified Coff

- Typically we will maintain around 30dB of isolation

- This determines Ron which is the dominate factor in insertion loss

- Wα Ron

Optimize Coff This Sets Insertion Loss

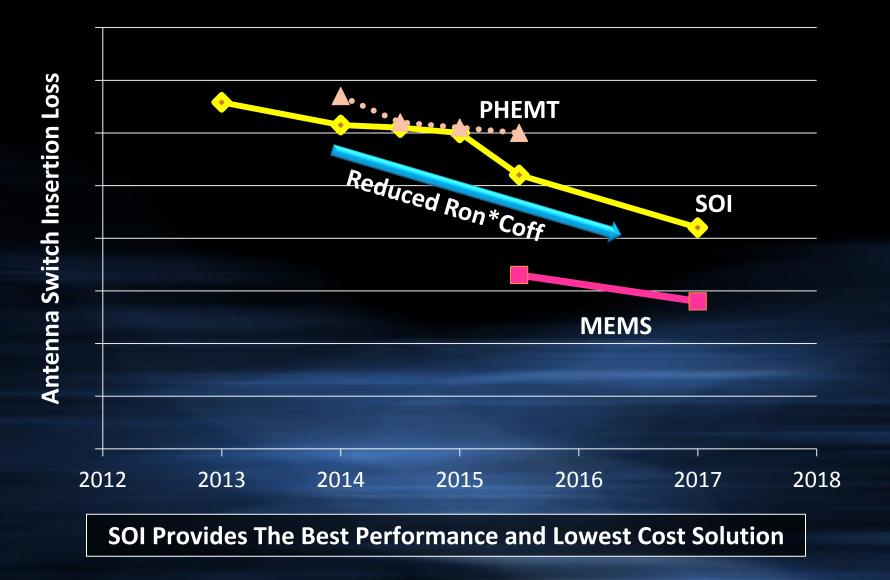

# SOI Ron\*Coff Process Improvement

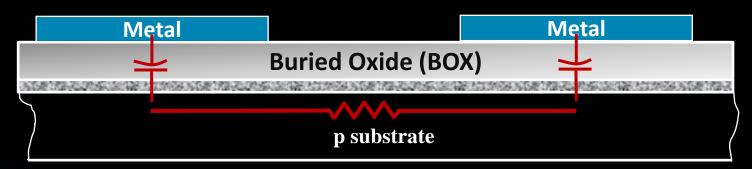

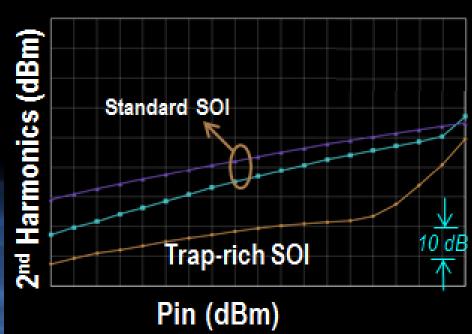

#### SOI Substrate: RF 2<sup>nd</sup> Harmonic

- Loss Decreases with Increasing Substrate Resistance

- − Typically use 1–10 kΩ/ $\square$

- Adding a Trap-rich Layer Reduces Loss and Improves Linearity

Managing and Reducing Substrate Parasitics Reduces Harmonics and IMD

#### **RF Switch Summary**

|                | SOI        | CMOS        | pHEMT                           | MEMS                        |

|----------------|------------|-------------|---------------------------------|-----------------------------|

| Insertion Loss | Acceptable | High        | Acceptable                      | Best                        |

| Linearity      | Acceptable | Acceptable? | Maybe<br>Better                 | Best                        |

| Integration    | Best       | Best        | Need an<br>External<br>CMOS Die | Requires<br>MEMS on<br>CMOS |

| Cost           | Acceptable | Best        | Higher                          | Very<br>Expensive<br>Today  |

**SOI Provides The Best Cost and Performance Solution**

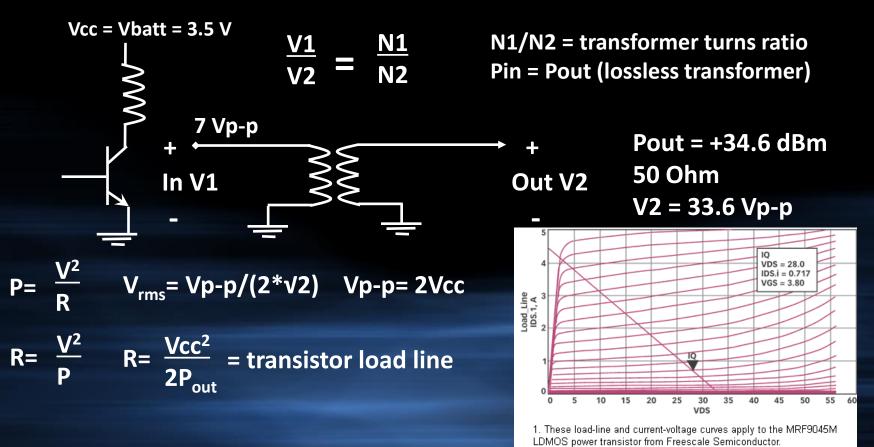

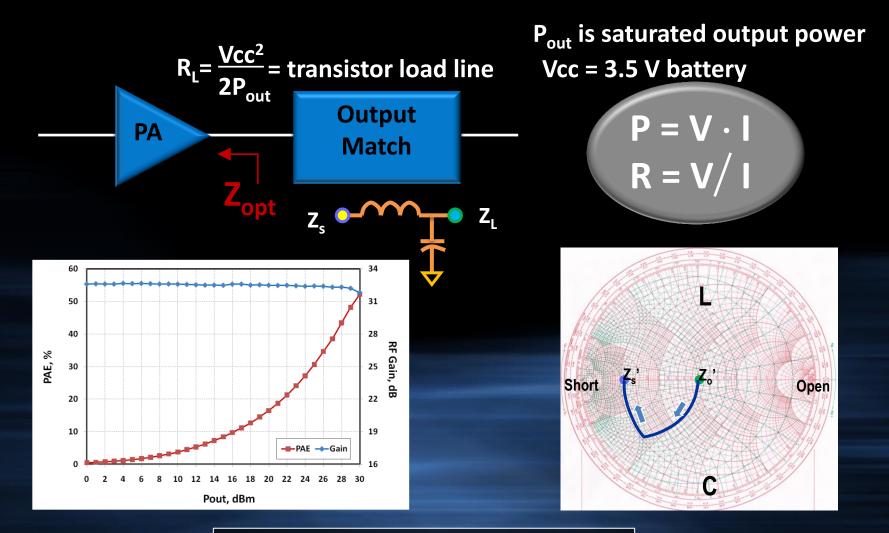

A Voltage Transformation

#### **Converting the Battery Voltage to RF Output Power**

**Output Match Steps Up RF Voltage**

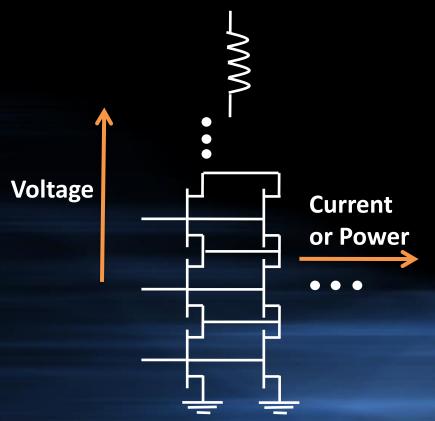

#### SOI Transistor PA Scaling

Vcc = Vbatt = 3.5 V

- Stacking Devices

- Based on the device breakdown voltage

- Shorter gate length: <u>more devices</u>

- Scale Width

- To support peak current

**Output Array Size Does Not Scale with Gate Length**

#### **PA Loadline Design**

Impedance Transformed with LPF

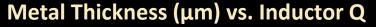

#### Metal Thickness vs. Inductor Q 2 GHz and 2–3 nH

On Die SOI Match is Costly and Provides Low Performance Relative to PCB

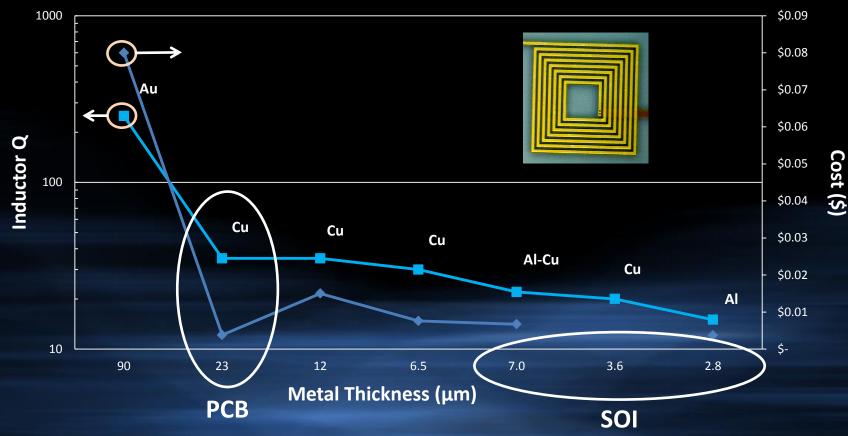

#### Output Match Network (OMN) Loss vs. Inductor Q

- 865 MHz, 3 Ohm Load Line

- Capacitor ESR = 0.05 Ohms

**Q** of the Inductor Determines the Loss

#### SOI/CMOS vs. GaAs HBT PAE

|              | Technology                                                                                                             | Drain or<br>Col. Eff.<br>η <sub>C2</sub> | Output Match<br>Loss η <sub>M2</sub> (dB) | Ga                              | Inter-stage<br>Loss ⴄო₂<br>(dB)      | Driver Eff.<br>η <sub>C1</sub> | PA PAE<br>Point A  |

|--------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------|---------------------------------|--------------------------------------|--------------------------------|--------------------|

|              | GaAs HBT                                                                                                               | 89%                                      | -0.65                                     | 14                              | -0.5                                 | 50%                            | 71%                |

|              | Measured HBT                                                                                                           |                                          |                                           |                                 |                                      |                                | 66%                |

|              | SOI                                                                                                                    | 75%                                      | -0.65                                     | 14                              | -0.5                                 | 40%                            | 60%                |

|              | Measured CMOS Amalfi[4]                                                                                                |                                          |                                           |                                 |                                      |                                | 50%                |

|              | Reported CMOS Nujira [5]                                                                                               |                                          | 57%                                       | 14                              | -0.5                                 | 40%                            | 54%                |

|              | SOI Carrara, Presti, et al. [6]                                                                                        | 72%                                      | -0.65                                     | 14                              | -0.5                                 | 40%                            | 57%                |

|              | CMOS 65nm [7]                                                                                                          | 70%                                      | -0.65                                     | 14                              | -0.5                                 | 40%                            | 56%                |

|              | Peregrine SOI PA [9]                                                                                                   | 72%                                      | -0.65                                     | 14                              | -0.5                                 | 40%                            | 57%                |

|              | SOI+on Die Match                                                                                                       | 75%                                      | -0.8                                      | 14                              | -0.5                                 | 40%                            | 58%                |

|              |                                                                                                                        |                                          |                                           |                                 |                                      | ax. Vcc,<br>ak Saturat         | ed Eff             |

|              | P <sub>II</sub>                                                                                                        | N RFIN                                   | A1                                        | Interstage<br>Match /<br>Filter | A2<br>Gutpu<br>Match<br>Filter       |                                | → P <sub>OUT</sub> |

| vs. SOI/CMOS | oile Handset PA Performance. ET vs. A<br>", 2014 International RF-SOI Worksho<br>ai, China; IWPC Chicago Meeting Sept. | p, Sept. 23,                             | івт †<br>G <sub>1</sub>                   |                                 | 1 1<br>G <sub>2</sub> η <sub>Μ</sub> | 2                              |                    |

SOI Device PA PAE Must Improve to Compete with GaAs HBT

|                  | SOI/CMOS    | GaAs HBT                             |

|------------------|-------------|--------------------------------------|

| Pout             | Acceptable  | Acceptable                           |

| PAE              | OK?         | ≈10% Better                          |

| Linearity        | Challenging | Best                                 |

| OMN Loss         | Higher      | External – Low Loss                  |

| Integration      | Best        | Requires External<br>CMOS Controller |

| Die Size         | 3–5X        | 1X                                   |

| PA Solution Cost | High        | Low                                  |

**GaAs HBT Provides the Lowest Cost with the Highest Performance**

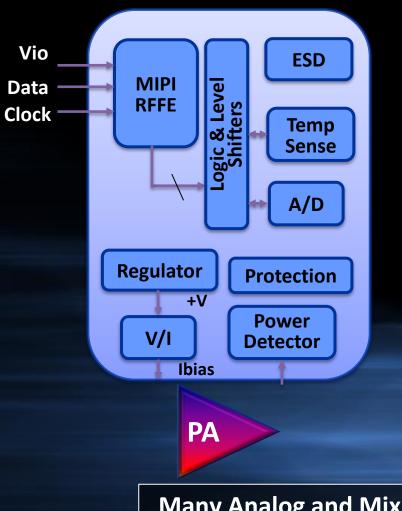

# Digital and Analog Sections PA Support

Analog / Mixed Signal Section RF Switch Example

**SKYWORKS**<sup>®</sup>

- Band gap

- Voltage regulator

- A/D

- V to I

- Temp. sensor

- Power detector

- MIPI

- ≈ 5K gates

- Needs a fine geometry to minimize size (<0.18 u)</li>

ESD Protection

Many Analog and Mixed Signal Circuits Required Place in a Low Cost CMOS Process

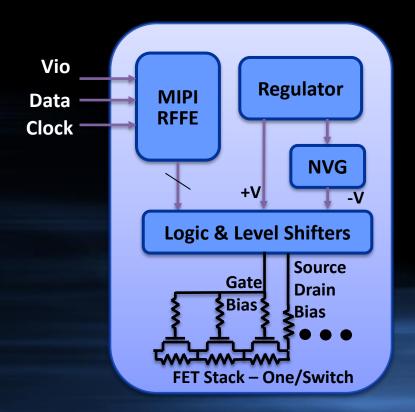

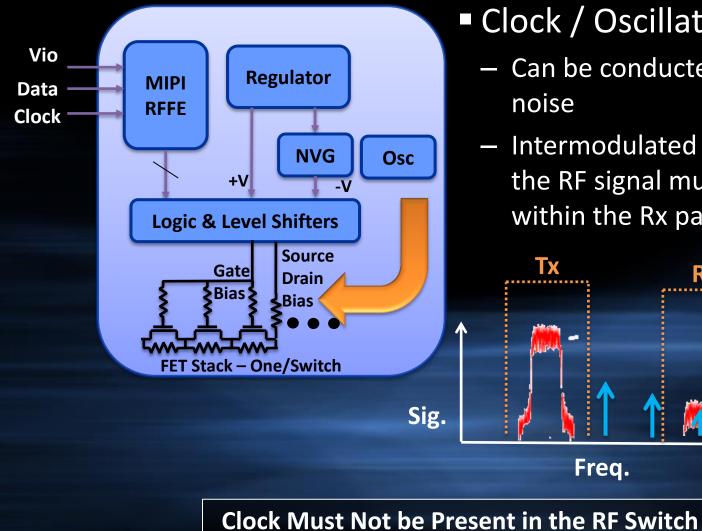

### Digital and Analog Sections RF Switch Support

- Analog / Mixed Signal

Section RF Switch Example

- Oscillator

- Band gap

- Voltage regulator

- Negative voltage generator

On the Die with the SOI Switch

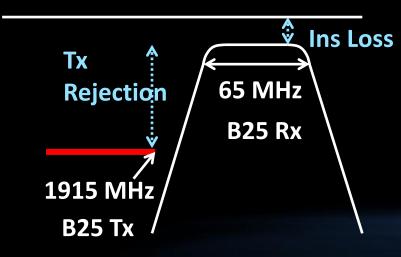

#### **B25 RX Band Pass Filter Analysis**

- Passband RX 1930–1995 MHz

- Rejection 1850–1915 MHz, >40 dB

#### Calculation

- W1=1930, W2=1995, Wt=1915

- W'/W<sub>1</sub>'= (2/ $\omega$ )((Wt -W0)/W0)=1.45

- Where  $\omega = 2(W2-W1)/(W2+W1) = 3.3\%$

- And W0=(2\*W2\*W1)/(W2+W1)=1961.96

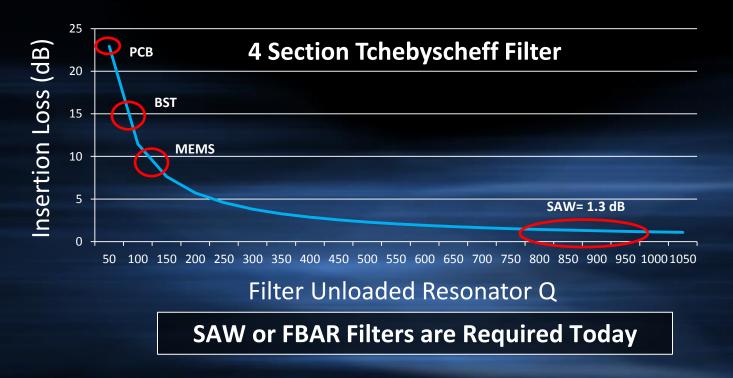

#### Filter

- 8 section 0.2 dB Tchebyscheff (0.5 dB Ripple 7 Section Filter)

- Tx rejection = 44 dB

#### Conclusion

- Using a MEMS Capacitor and Inductor Tunable Filter

Unloaded combined Q of 100

- SAW Filters Provide the Q Necessary for a Low Insertion Loss

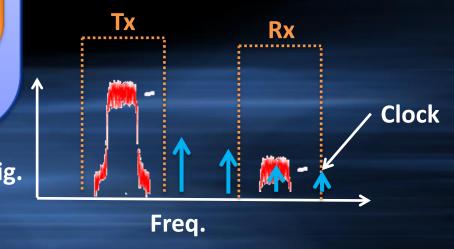

#### **Clock Isolation**

#### Clock / Oscillator Noise

- Can be conducted or radiated

- Intermodulated clock noise onto the RF signal must be <110 dBm within the Rx passband

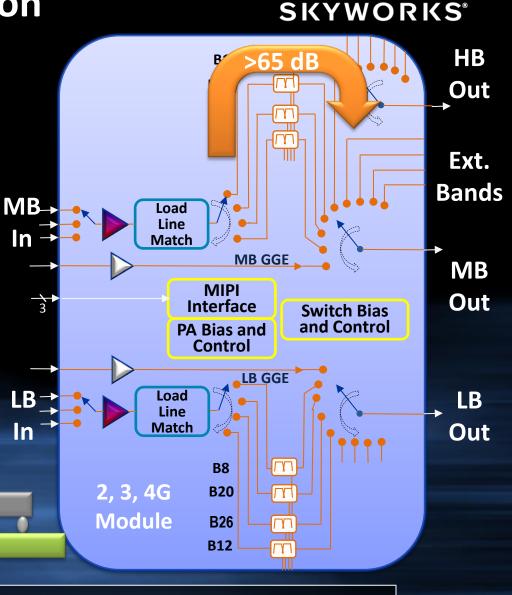

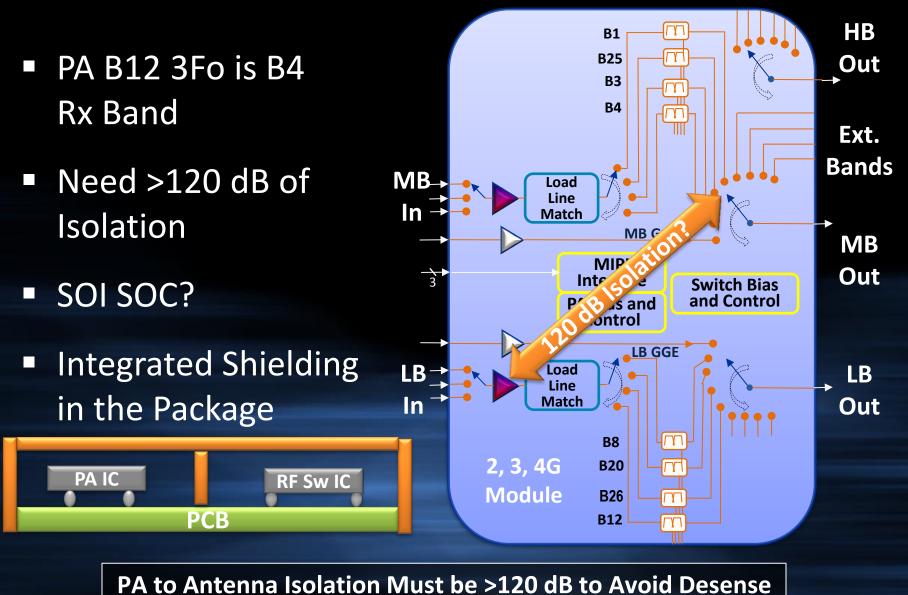

#### **Tx to Antenna Isolation**

- Duplexer Tx to Ant Typically has >55 dB of Isolation

- SOI IC Should Have >65 dB of Isolation

- Typically Only Accomplished with a Flipped Chip Package and Careful Design of Routing

- This is Only One of Many RF Isolation Requirements in the Design

SOI

PCB

TX to Antenna Isolation Must be >65 dB to Avoid Desense

**SKYWORKS**<sup>®</sup>

#### **Tx to Antenna Isolation**

# Design, Simulation and Test with High Integration

SKYWORKS

<u>SOI Process</u> Ron\*Coff Thick Metal

Linear Substrate High Isolation

#### **Interconnect**

Flip Chip On Substrate Integrated Shield Transmission Lines

**Functions**

PA RF Switch Power Control and MIPI Analog/Mixed Signal Filters ESD Protection Sim. and Des. Tools Harmonic Balance Transient 2D/3D EM RTL Compiler NCSIM (Digital Sim.)

#### <u>Layout</u>

DRC, LVS, Antenna Auto Router, Digital and Analog

<u>Full Functional</u> <u>RF Test</u> Automated Automated Data Analysis

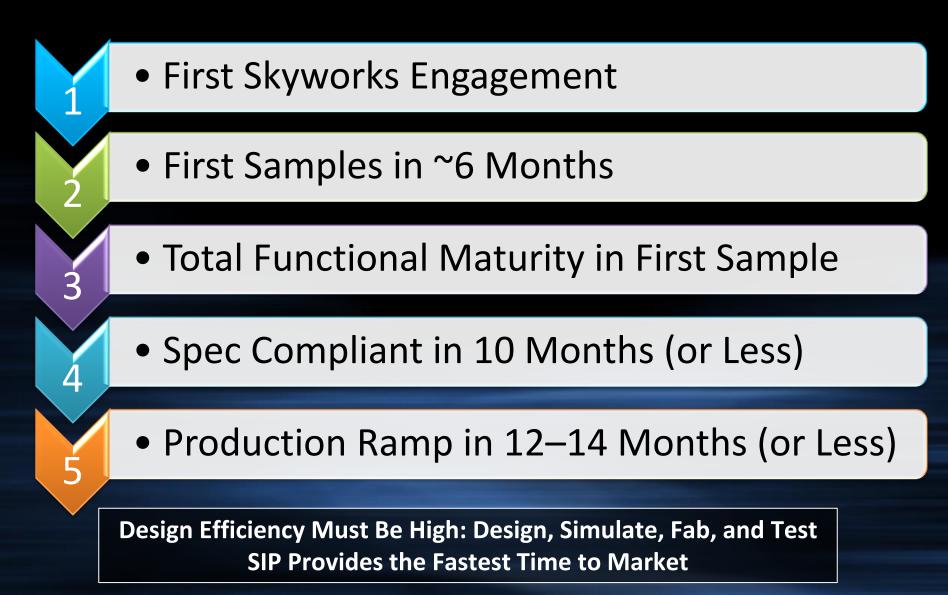

#### Extremely Difficult and Time Consuming to Design, Test, and Analyze

#### **Customer's Expectation**

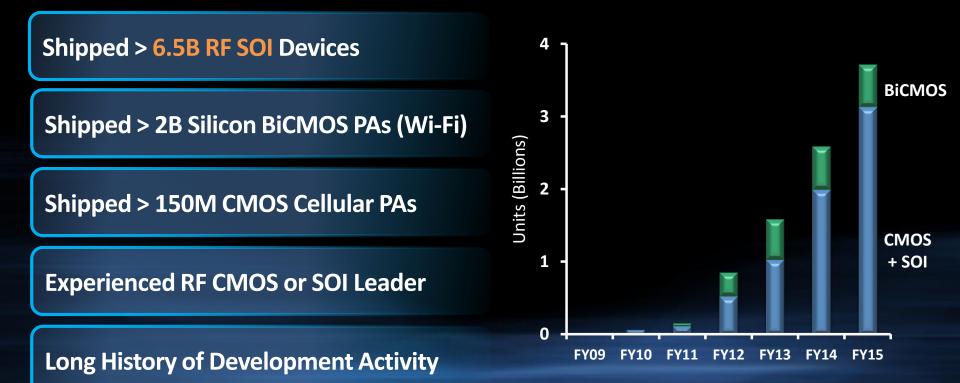

#### RF SOI, RF CMOS, and BiCMOS Skyworks Shipments

SOI is Clearly a Big Part of the Growing Mobile Market

#### Summary – The Best Solution

| Block             | Technology<br>of Choice | Primary<br>Reason |

|-------------------|-------------------------|-------------------|

| РА                | GaAs HBT                | PAE and Cost      |

| PA OMN            | РСВ                     | Low Loss/ High Q  |

| PA Controller     | CMOS                    | Cost              |

| RF Switch         | SOI                     | Cost/Performance  |

| Switch Controller | CMOS/SOI                | Cost              |

| MIPI RFFE         | CMOS                    | Cost              |

| Filters           | SAW/FBAR                | High Q            |

SIP Wins Based on Cost, Performance and Time to Market

- [1] F. Raab, P. Asbeck, S. Cripps, P. Kenington, Z. Popovic, N. Pothecary, J. Sevic, N Sokal, "Power Amplifiers and Transmitters for RF and Microwave", IEEE Transactions on Microwave Theory and Techniques, Vol. 50 No. 3, March 2002

- [2] F. Raab, "Maximum Efficiency and Output of Class-F Power Amplifiers," IEEE Transactions on Microwave Theory and Techniques, Vol. 49, NO. 6, June 2001.

- [3] J. Young, N. Cheng, "MULTIMODE MULTIBAND POWER AMPLIFIER OPTIMIZATION FOR MOBILE APPLICATIONS" IEEE VLSI\_TSA CONFERENCE, APRIL 23 2013

- [4] Hee-Soo Lee, Andy Howard, "RF Power Amplifier Design Series Part 4: RF Module Design using Amalfi CMOS PA" 2012 Agilent Technologies, Inc., Webcast

- [5] "Envelope Tracking: Unlocking The Potential Of CMOS PAs In 4G Smart Phones" Nujira White Paper, Feb. 2013

- [6] F.Carrara, C.D. Presti, G. Palmisano, A Scuderi "Power Transistor Design Guidelines and RF Load-Pull Characterization of a 0.13-um SOI CMOS Technology"

- [7] S. Leuschner, et al. "A 31dBm, High Ruggedness Power Amplifier in 65nm Standard CMOS with High-Efficiency Stacked-Cascode Stages", 2010 IEEE Radio Frequency Integrated Circuit Symposium, RTU1C-3

- [8] J. Young, D. Ripley, P. Lehtola, "Envelope Tracking Power Amplifier Optimization for Mobile Applications", 2013 IEEE S3S Conference

- [9] N Comfoltey, D Kelly, D Nobbe, . Olson, "State-of-the-Art of RF Front-End Integration in SOI CMOS", 2013 IEEE S3S Conference

- [10] L. Formenti "ST H9SOI\_FEM: 0.13 RFSOI Technology for Front End Module Monolithic Integration", International RF SOI Workshop, Sept. 2014

Skyworks Solutions, Inc. Proprietary and Confidential Information