C Soitec

# RF Performance of Passive Components on State-of-Art Trap Rich Silicon-on-Insulator Substrates

STTRY 上海微技木工业研究院 Standart sundar Research Institute

2016/7/22

# Outline

- Introduction on RF SOI Technology

- Soitec-SITRI Joint Development Program on RF SOI Technology

- CPW lines integrated on the HR-SOI and RFeSI substrates

- Small signal characteristics: attenuation characteristic, and temperature effect on it

- Large signal characteristics: the 2<sup>nd</sup> and 3<sup>rd</sup> harmonic, and temperature effect on them

- Spiral inductors integrated on the HR-SOI and RFeSI substrates.

- Conclusion

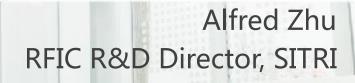

#### RF Front End Evolution (from 2G to 4G) --access to what you want, when you want and where you want

LTE

Courtesy of Soitec

ortec

- More antennas  $\rightarrow$  MIMO

- More frequency bands  $\rightarrow$  high performance high-throw switches

$\rightarrow$  more low-throw switches  $\rightarrow$  more PAs, more filters • Package (SIP) and module integration

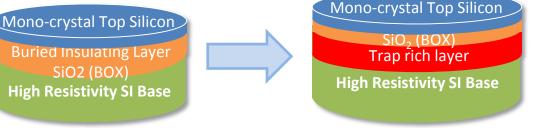

#### Soitec RFeSI Products Enabling Performance to The RF Function

| Cellular roadmap always requires more linearity |                         |  |  |  |

|-------------------------------------------------|-------------------------|--|--|--|

| Network                                         | Linearity (IIP3 in dBm) |  |  |  |

| 2G                                              | 2G 55                   |  |  |  |

| 3G                                              | 65                      |  |  |  |

| 4G LTE                                          | 72                      |  |  |  |

| 4G LTE + CA                                     | Up to 90                |  |  |  |

Source: Intel Mobile, L. Schumacher, Nov. 2012

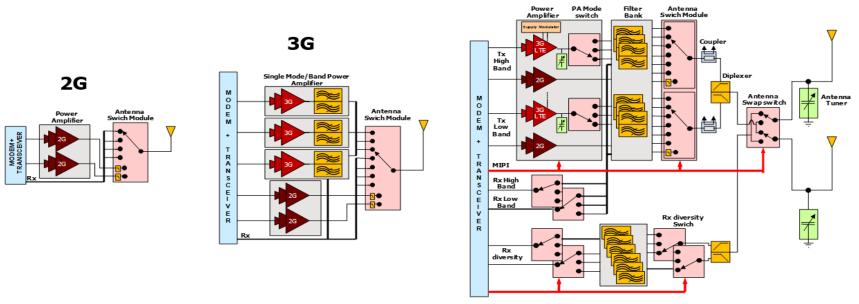

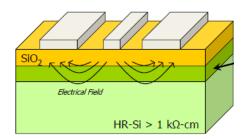

#### A trap rich layer is added to the standard

#### **HR-SOI** substrate

RFeSI SOI substrate

#### • Improve all RF critical parameters

Home | News | Press releases

| > | Press releases     |

|---|--------------------|

| 1 | 2016               |

| 1 | > 2015             |

| 1 | > 2014             |

| - | > 2013             |

| 1 | > 2012             |

| > | Soitec in the news |

| > | ndustry news       |

| > | Events             |

#### Soitec and Shanghai Industrial µTechnology research institute (SITRI) announce collaboration on highperformance RF-SOI technology

Aim is to develop next-generation SOI communication solutions focusing on the fast-developing Chinese RF ecosystem

Bernin (Grenoble), France and Shanghai, China, June 9th, 2015— Soitec (Euronext), a world leader in generating and manufacturing revolutionary semiconductor materials for the electronics and energy industries, and Shanghai Industrial µTechnology Research Institute (SITRI), a leader in "More than Moore" technology R&D and commercialization, announced today the signature of a collaboration agreement. The strategic partnership will enable both Soitec and SITRI to strengthen their leadership in high-growth wireless communications and the global market for radio-frequency (RF) applications, with a special emphasis on the fast-developing Chinese RF ecosystem.

The joint collaboration announced today focuses on developing RF-SOI (Silicon On Insulator) technology using advanced circuit designs based on Soitec's substrate materials and technologies.

"Experience shows that Soitec's engineered substrates can optimize RF-SOI technology and applications in terms of both cost competitiveness and power efficiency. This strategic partnership will enable us to push the limits of RF circuits and meet future connectivity needs," said Carlos Mazure, chief technical officer of Soitec.

"Enhancing RF signal integrity is a key focus of the mobile communications industry as it builds toward 4G-LTE Advanced and 5G standards. We are excited to partner with Soitec in developing next-generation SOI communication solutions. It is consistent with SITRI's mission to create a collaborative R&D and commercialization environment to catalyze the growth of advanced technologies," said Dr. Charles Yang, president of SITRI.

Follow us on Twitter

> twitter.com/Soitec\_EN

#### Contact

If you are looking for more information, please contact our International Media Relations:

Trade press: > Camille Dufour

Business press: > Marylen Schmidt

7

SITRI CONFIDENTIAL © 2016 All Rights Reserved

#### Soitec-SITRI Joint Development Program on High Performance RF SOI Technology

Joint collaboration between SITRI and Soitec for research and development of RF SOI technology solutions including device, circuit design and RF CMOS technology

Various substrates RF performance

High performance passive RF Devices RF MEMS? III-V on Silicon? New technologies?

RF substrates for 5G applications

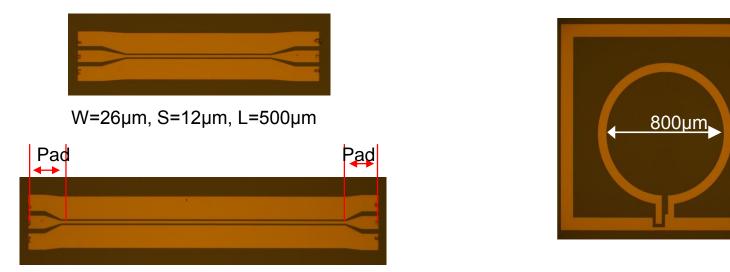

## **Fabricated Passive Devices on RF-SOI Substrates**

W=26µm, S=12µm, L=2176µm

| Substrates | ρ (kΩ·cm) of<br>bulk Si | ρ (kΩ·cm)<br>bellow BOX | t <sub>ox</sub> (µm) | t <sub>Si</sub> (µm) |

|------------|-------------------------|-------------------------|----------------------|----------------------|

| HR-SOI     | 5.6                     | NAN                     | 0.4                  | 725                  |

| RFeSI G1   | >10                     | 6.5                     | 0.4                  | 725                  |

| RFeSI 90   | >10                     | 16.7                    | 0.4                  | 725                  |

Metal stack is 500nm Al and 500nm Au.

C Soitec

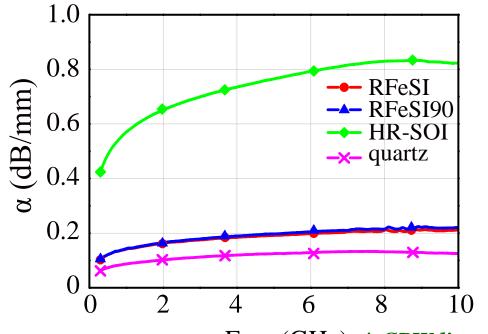

## Measurement Results of CPW Transmission Lines: Attenuation Factor

Freq (GHz) \* CPW line size are: 26, 12 and 208 um.

oitec

• RFeSI substrates present much reduced losses compared with HR-SOI substrates, while RFeSI and RFeSI90 substrates show almost same loss.

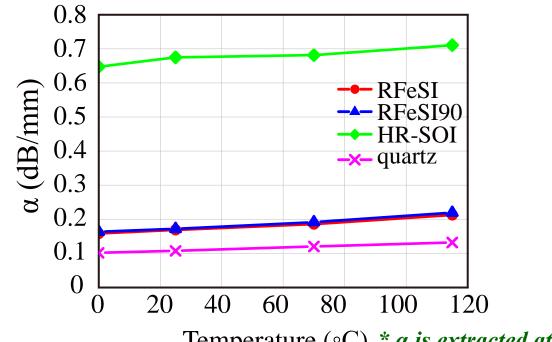

## Measurement Results of CPW Transmission Lines: Temperature Effect on Attenuation Factor

Temperature ( $\circ$ C) \*  $\alpha$  is extracted at 2.45 GHz.

oitec

• Increased α with raising temperature is predominated by the increasing metal loss.

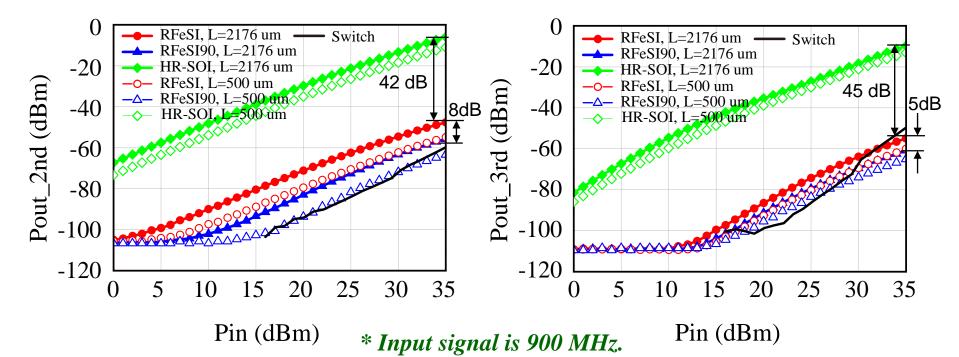

#### Measurement Results of CPW Transmission Lines: 2<sup>nd</sup> and 3<sup>rd</sup> Harmonics

• CPW lines with 2176 um and 500 um length and an SPDT switch using a commercial 0.18 um RF-SOI process are compared.

- RFeSI90 substrates shows the best harmonic suppression.

- Shorter CPW lines have better harmonic suppression due to less coupling to the substrate.

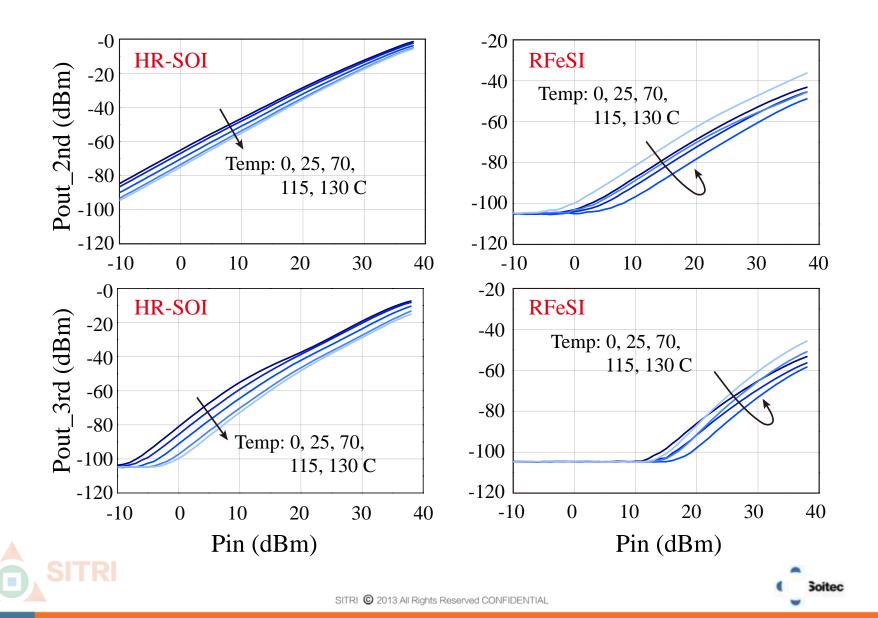

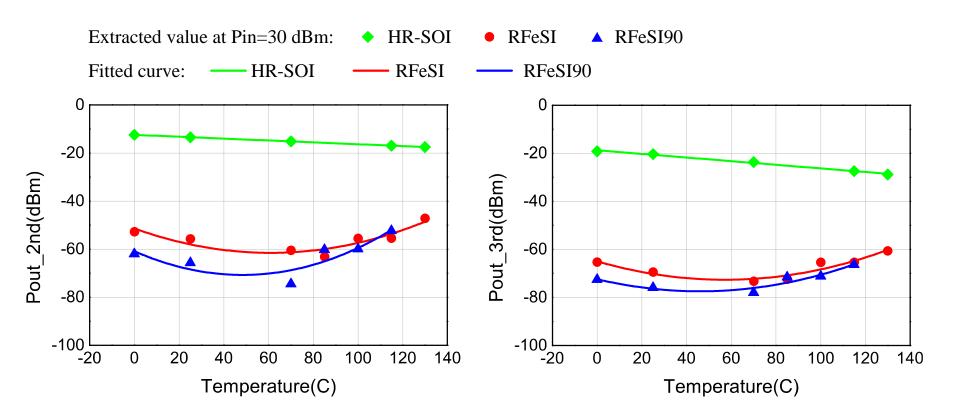

## Measurement Results of CPW Transmission Lines: Temperature Effect on 2<sup>nd</sup> and 3<sup>rd</sup> Harmonics

#### Measurement Results of CPW Transmission Lines: Temperature Effect on 2<sup>nd</sup> and 3<sup>rd</sup> Harmonics

Extracted 2<sup>nd</sup> and 3<sup>rd</sup> harmonics when Pin=30 dBm

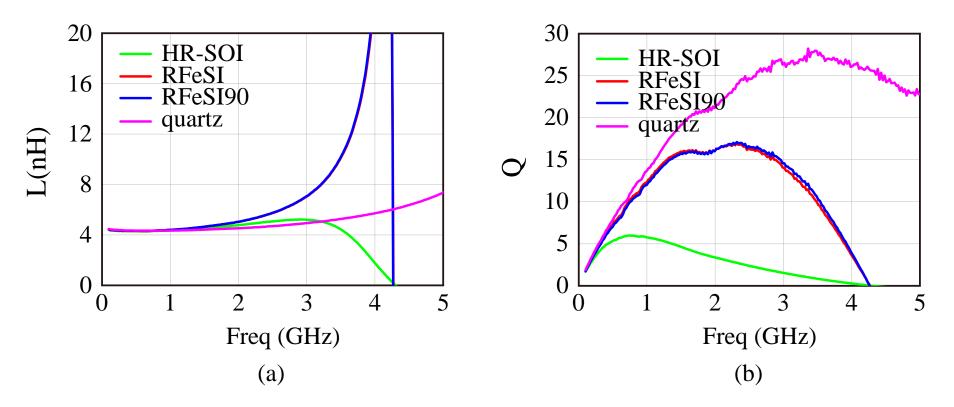

## Measurement Results of Spiral Inductors: Inductance and Quality-Factor

• The inductors on RFeSI substrates show much higher Q than those on HR-SOI ones, while RFeSI and RFeSI90 substrates show similar inductor performance.

ortec

## Conclusion

- The CPW lines fabricated on RFeSI and RFeSI90 substrates show superior RF performance, i.e. lower attenuation and harmonics, compared to those on the HR-SOI substrate.

- α increases with increasing temperature for both HR-SOI and RFeSI substrates.

- RFeSI90 substrates show the best harmonic performance among HR-SOI, RFeSI and RFeSI90 substrates.

- The spiral inductors fabricated on RFeSI and RFeSI90 substrates present much larger Q than those on the HR-SOI substrate.

# **Thank You !**

SITRI © 2013 All Rights Reserved CONFIDENTIAL